Check out my first novel, midnight's simulacra!

Transmeta processors: Difference between revisions

Jump to navigation

Jump to search

No edit summary |

No edit summary |

||

| (15 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

[[File:Transmeta-corp-logo.JPG|thumb|right|Transmeta Corporation logo]] | |||

* [[:File:Tm8300tm8600.pdf|TM8300/TM8600 product spec]] | * [[:File:Tm8300tm8600.pdf|TM8300/TM8600 product spec]] | ||

* [[:File:Tm3200.pdf|TM3200 product spec]] | * [[:File:Tm3200.pdf|TM3200 product spec]] | ||

| Line 4: | Line 5: | ||

{| border="1" | {| border="1" | ||

! Family | ! Family | ||

! Model | ! Model | ||

! Interface | ! Interface | ||

! Frequencies | ! Frequencies | ||

! L1 | ! L1 Caches | ||

! L2 Cache | ! L2 Cache | ||

! TLB | ! TLB | ||

| Line 14: | Line 14: | ||

! Peripherals | ! Peripherals | ||

|- | |- | ||

| rowspan="2" | Crusoe | | rowspan="2" | Crusoe (128-bit + MMX) | ||

| | |||

[[File:Tm5400_chip.jpg|thumb|right|TM5400]] | |||

2x ALU, 1x Load/Store | |||

1x Branch, 1x FP/MM | |||

| TM3200 | | TM3200 | ||

| BGA-474 | | BGA-474 | ||

| Line 31: | Line 37: | ||

| 64K 8-associative code, | | 64K 8-associative code, | ||

64K 16-associative data | 64K 16-associative data | ||

| 256K unified | | 256K 4-associative unified | ||

| 256 entries, 4-associative | | 256 entries, 4-associative | ||

| SDR/DDR SDRAM 66--133MHz, | | SDR/DDR SDRAM 66--133MHz, | ||

DDR SDRAM 100--133MHz | DDR SDRAM 100--133MHz | ||

| 33MHz 32-bit | | 33MHz 32-bit PCI | ||

|- | |- | ||

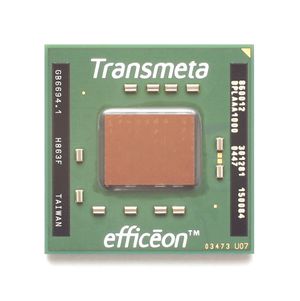

| ROWSPAN="5" | Efficeon | | ROWSPAN="5" | Efficeon (256-bit + SSE2) | ||

[[File:KL_Transmeta_Efficeon_8600.jpg|thumb|right|TM8600]] | |||

2x ALU, 2x Load/Store/Add | |||

2x Execute, 2x FP/MM/SSE/SSE2 | |||

1x Branch, 1x Alias, 1x Control | |||

| TM8300 | | TM8300 | ||

| BGA-783 | | BGA-783 | ||

| Line 66: | Line 79: | ||

| 1M 4-associative unified | | 1M 4-associative unified | ||

| 256 entries, 4-associative | | 256 entries, 4-associative | ||

| | | 100--200MHz DDR SDRAM + SPD | ||

| 400MHz HyperTransport, AGP 1x/2x/4x | | 400MHz HyperTransport, AGP 1x/2x/4x | ||

|- | |- | ||

| Line 76: | Line 89: | ||

| 1M 4-associative unified | | 1M 4-associative unified | ||

| 256 entries, 4-associative | | 256 entries, 4-associative | ||

| | | 100--200MHz DDR SDRAM + SPD | ||

| 400MHz HyperTransport, AGP 1x/2x/4x | | 400MHz HyperTransport, AGP 1x/2x/4x | ||

|- | |- | ||

| Line 86: | Line 99: | ||

| 1M 4-associative unified | | 1M 4-associative unified | ||

| 256 entries, 4-associative | | 256 entries, 4-associative | ||

| | | 100--200MHz DDR SDRAM + SPD | ||

| 400MHz HyperTransport, AGP 1x/2x/4x | | 400MHz HyperTransport, AGP 1x/2x/4x | ||

|} | |} | ||

==See Also== | ==See Also== | ||

* The [http://www.sandpile.org/docs/tmta.htm sandpile] has a fine Transmeta collection | * The [http://www.sandpile.org/docs/tmta.htm sandpile] has a fine Transmeta doc collection | ||

** And a [http://www.sandpile.org/impl/crusoe.htm Crusoe] reference | |||

** Not to mention an [http://www.sandpile.org/impl/efficeon.htm Efficeon] reference | |||

* A good [http://hubpages.com/hub/Ball-Grid-Array-Guide BGA page] at HubPages. | |||

[[CATEGORY: Hardware]] | |||

[[CATEGORY: X86]] | |||

Latest revision as of 16:30, 17 April 2010