Check out my first novel, midnight's simulacra!

Ivy Bridge: Difference between revisions

Jump to navigation

Jump to search

No edit summary |

|||

| Line 1: | Line 1: | ||

A 22nm update to [[Sandy Bridge]], scheduled for release in late 2012. This will be the first chip to feature Intel's new "FinFET" [http://en.wikipedia.org/wiki/Multigate_device#Tri-gate_transistors_.28Intel.29 trigate] nonplanar transistor technology. Its Panther Point chipset is expected to support [[PCIe|PCIe 3.0]], while the IGD will add DirectX 11 and [[OpenCL|OpenCL 1.1]] support. Ivy Bridge is expected to continue making use of the LGA1155 socket interface introduced with Sandy Bridge. | A 22nm update to [[Sandy Bridge]], scheduled for release in late 2012. This will be the first chip to feature Intel's new "FinFET" [http://en.wikipedia.org/wiki/Multigate_device#Tri-gate_transistors_.28Intel.29 trigate] nonplanar transistor technology. Its Panther Point chipset is expected to support [[PCIe|PCIe 3.0]], while the IGD will add DirectX 11 and [[OpenCL|OpenCL 1.1]] support. Ivy Bridge is expected to continue making use of the LGA1155 socket interface introduced with Sandy Bridge. | ||

==Architecture== | ==Architecture== | ||

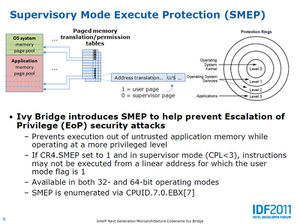

[[File:Smep.jpeg|right|thumb|IDF 2011 slide on SMEP]] | |||

* The [[RDRAND]] instruction is made available on Ivy Bridge processors containing Bull Mountain hardware. | * The [[RDRAND]] instruction is made available on Ivy Bridge processors containing Bull Mountain hardware. | ||

* Supervisory Mode Execution Protection (SMEP) prohibits ring 0 code from executing memory writable by other rings | * Supervisory Mode Execution Protection (SMEP) prohibits ring 0 code from executing memory writable by other rings | ||

==Microarchitecture== | ==Microarchitecture== | ||

Microarchitecture is expected to be similar to that of [[Sandy Bridge]]. | Microarchitecture is expected to be similar to that of [[Sandy Bridge]]. | ||

Latest revision as of 22:26, 18 October 2011

A 22nm update to Sandy Bridge, scheduled for release in late 2012. This will be the first chip to feature Intel's new "FinFET" trigate nonplanar transistor technology. Its Panther Point chipset is expected to support PCIe 3.0, while the IGD will add DirectX 11 and OpenCL 1.1 support. Ivy Bridge is expected to continue making use of the LGA1155 socket interface introduced with Sandy Bridge.

Architecture

- The RDRAND instruction is made available on Ivy Bridge processors containing Bull Mountain hardware.

- Supervisory Mode Execution Protection (SMEP) prohibits ring 0 code from executing memory writable by other rings

Microarchitecture

Microarchitecture is expected to be similar to that of Sandy Bridge.

Branding/Differentiation

Processor Support

Ivy Bridge will introduce the "Panther Point" 7-series PCH (Platform Controller Hub), and the second-tier "Patsburg" X79 (this latter will use DMI rather than QPI). Native USB 3.0 and PCIe 3.0 support is expected on-chip.

See Also

- "Inside the Intel Ivy Bridge Microarchitecture" at www.hardwaresecrets.com