Check out my first novel, midnight's simulacra!

Dot: Difference between revisions

Jump to navigation

Jump to search

| Line 9: | Line 9: | ||

label="Quad-Core Opteron" | label="Quad-Core Opteron" | ||

node [shape=record]; | node [shape=record]; | ||

struct3 [label="{ {C0|C1|C2|C3}|{L1/L2|L1/L2|L1/L2|L1/L2}|SRI (SysReq Interface)|<xbar>XBAR (Crossbar Switch)|{MCH|ncHT-HB|HT0|HT1}}"]; | struct3 [label="{ {C0|C1|C2|C3}|{L1/L2|L1/L2|L1/L2|L1/L2}|SRI\ | ||

(SysReq Interface)|<xbar>XBAR (Crossbar Switch)|{MCH|ncHT-HB|HT0|HT1}}"]; | |||

} | } | ||

} </pre> | } </pre> | ||

Revision as of 11:55, 26 January 2010

SVG

- graphviz tools generate svg via -Tsvg

- notugly is some XSL to beautify dot's SVG output

Examples

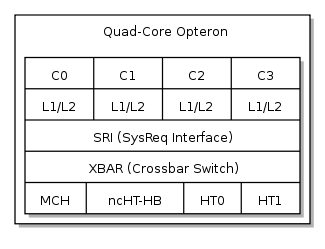

Packed Record

digraph G {

subgraph clusterOpteron {

label="Quad-Core Opteron"

node [shape=record];

struct3 [label="{ {C0|C1|C2|C3}|{L1/L2|L1/L2|L1/L2|L1/L2}|SRI\

(SysReq Interface)|<xbar>XBAR (Crossbar Switch)|{MCH|ncHT-HB|HT0|HT1}}"];

}

}

Rectilinear arrangement A

digraph G {

subgraph clusterOpteronNUMA {

label = "2x 'Deneb' Phenom II X4 910 (45nm, AM3). 8 threads."

Deneb0->Deneb1 [dir="both" label="2GHz 16-bit bidir\n8GB/s HyperTransport 3.0" color="blue"]

DDR0 -> Deneb0 [dir="both" color="lightblue"]

DDR1 -> Deneb1 [dir="both" color="lightblue"]

HostBus -> Deneb0 [dir="both" color="darkgreen"]

HostBus -> Deneb1 [dir="both" color="darkgreen"]

{ rank=same; Deneb0 Deneb1 }

{ rank=same; DDR0 DDR1 }

Deneb0 [style=filled fillcolor=steelblue shape=box]

Deneb1 [style=filled fillcolor=steelblue shape=box]

DDR0 [style=filled fillcolor=grey shape=invhouse]

DDR1 [style=filled fillcolor=grey shape=invhouse]

HostBus [style=filled fillcolor=green shape=Msquare]

}

}

Rectilinear arrangement B

digraph G {

nodesep="1"

subgraph clusterNehalemSMP {

DDR0 -> Nehalem0 [dir="both" color="lightblue"]

DDR0 -> Nehalem1 [dir="both" color="lightblue"]

Nehalem0->Nehalem1 [dir="both" label="25.6GB/s QuickPath" color="blue"]

subgraph clusterNehalemSMP0 {

label="DRAM may or may not be shared.";

style=filled;

color=lightgrey;

{ rank=same; DDR0 }

{ rank=same; Nehalem0 Nehalem1 }

}

Nehalem2->Nehalem3 [dir="both" label="25.6GB/s QuickPath" color="blue"]

Nehalem2 -> DDR1 [dir="both" color="lightblue"]

Nehalem3 -> DDR1 [dir="both" color="lightblue"]

subgraph clusterNehalemSMP1 {

labelloc="b";

label="Each package gets its own MCH and L3 cache,\neach core its own (split) L1 and (unified) L2.";

style=filled;

color=lightgrey;

{ rank=same; Nehalem2 Nehalem3 }

{ rank=same; DDR1 }

}

label = "4x 'Nehalem-EP' E5520 HT Core i7 (45nm LGA1336). 32 threads."

Nehalem1->Nehalem2 [dir="both" color="blue"]

Nehalem3->Nehalem0 [dir="both" color="blue"]

Nehalem0->HostBus [dir="both" color="darkgreen"]

Nehalem1->HostBus [dir="both" color="darkgreen"]

HostBus->Nehalem2 [dir="both" color="darkgreen"]

HostBus->Nehalem3 [dir="both" color="darkgreen"]

Nehalem0 [style=filled fillcolor=steelblue shape=box label="4x 2-way cores"]

Nehalem1 [style=filled fillcolor=steelblue shape=box label="4x 2-way cores"]

Nehalem2 [style=filled fillcolor=steelblue shape=box label="4x 2-way cores"]

Nehalem3 [style=filled fillcolor=steelblue shape=box label="4x 2-way cores"]

DDR0 [style=filled fillcolor=grey shape=invtrapezium]

DDR1 [style=filled fillcolor=grey shape=trapezium]

HostBus [style=filled fillcolor=green shape=Msquare]

}

}